180x Filetype PPT File size 0.27 MB Source: users.ece.utexas.edu

Outline

Signal processing applications

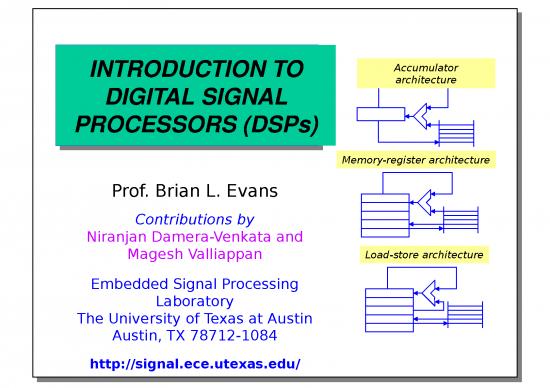

Conventional DSP architecture

Pipelining in DSP processors

RISC vs. DSP processor architectures

TI TMS320C6000 DSP architecture

introduction

Signal processing on general-purpose

processors

Conclusion

2 -2

Signal Processing Applications

Embedded system demand: volume, volume, …

400 Million units/year: automobiles, PCs, cell phones

30 Million units/year: ADSL modems and printers

Embedded system cost and input/output rates

Low-cost, medium-throughput: low-end printers,

handsets, sound cards, car audio, disk drives Single

DSP

High-cost, high-throughput: high-end printers,

wireless basestations, 3-D sonar, 3-D images fromMultiple

2-D X-rays (tomographic reconstruction) DSPs

Embedded processor requirements

Inexpensive with small area and volume

Predictable input/output (I/O) rates to/from processor

Power constraints (severe for handheld devices)

2 -3

Conventional DSP Processors

Low cost: $3/processor in volume

Deterministic interrupt service routine latency

guarantees predictable input/output rates

On-chip direct memory access (DMA) controllers

Processes streaming input/output separately from CPU

Sends interrupt to CPU when block has been read/written

Ping-pong buffering

CPU reads/writes buffer 1 as DMA reads/writes buffer 2

After DMA finishes buffer 2, roles of buffers 1 & 2 switch

Low power consumption: 10-100 mW

TI TMS320C54 0.32 mA/MIP 76.8 mW at 1.5 V, 160 MHz

TI TMS320C55 0.05 mA/MIP 22.5 mW at 1.5 V, 300 MHz

Based on conventional (pre-1996) architecture

2 -4

Conventional DSP Architecture

Multiply-accumulate (MAC) in 1 instruction cycle

Harvard architecture for fast on-chip I/O

Data memory/bus separate from program memory/bus

One read from program memory per instruction cycle

Two reads/writes from/to data memory per inst. cycle

Instructions to keep pipeline (3-6 stages) full

Zero-overhead looping (one pipeline flush to set up)

Delayed branches

Special addressing modes supported in hardware

Bit-reversed addressing (e.g. fast Fourier transforms)

Modulo addressing for circular buffers (e.g. FIR filters)

2 -5

Conventional DSP Architecture (con’t)

Data Shifting Using a Linear Buffer

Buffer of length K

Time Buffer contents Next sample

Used in finite and x x x x x

n=N N-K+1 N-K+2 N-1 N N+1

infinite impulse

response filters x x x x

n=N+1 N-K+2 N-K+3 N N+1 xN+2

Linear buffer

xN-K+3 x xN+1 x

Sort by time index n=N+2 N-K+4 N+2 xN+3

Update: discard

oldest data, copy

old data left, insert Modulo Addressing Using a Circular Buffer

new data Time Buffer contents Next sample

Circular buffer

n=N x x x x x x

Oldest data index N-2 N-1 N N-K+1 N-K+2 N+1

Update: insert new n=N+ x x xx x x x xN+2

N-2 N-1 NN N+1 N-K+2 N-K+3

data at oldest 1

index, update x x x

x x x x x

N-2 N N+1 x

N-1 N N+2 N-K+3 N-K+4

n=N+2 N-K+4 x

oldest index N+3

2 -6

no reviews yet

Please Login to review.